1、射频LNA设计要求

低噪声放大器(LNA)作为射频信号传输链路的第一级,它的噪声系数特性决定了整个射频电路前端的噪声性能,因此作为高性能射频接收电路的第一级LNA的设计必须满足[1]:(1)较高的线性度以抑制干扰和防止灵敏度下降;(2)足够高的增益,使其可以抑制后续级模块的噪声;(3)与输入输出阻抗的匹配,通常为50Ω;(4)尽可能低的功耗,这是无线通信设备的发展趋势所要求的。

2、Inductive degenerate cascode结构LNA

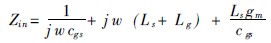

Inductive-degenerate cascode结构是射频LNA设计中使用比较多的结构之一[2],因为这种结构能够增加LNA的增益,降低噪声系数,同时增加输入级和输出级之间的隔离度,提高稳定性。Inductive-degenerate cascode结构在输入级MOS管的栅极和源极分别引入两个电感Lg和Ls,通过选择适当的电感值,使得输入回路在电路的工作频率附近产生谐振,从而抵消掉输入阻抗的虚部。在图1中LNA的输入阻抗为:

(1)

(1)

当处于谐振状态时: (2)

(2)

那么: (3)

(3)

输入阻抗呈现纯电阻特性,其值由Ls和 确定。由分析可知应用Inductive-degenerate cascode结构输入阻抗得到一个50Ω的实部,但是这个实部并不是真正的电阻,因而不会产生噪声,所以很适合作为射频LNA的输入极。

确定。由分析可知应用Inductive-degenerate cascode结构输入阻抗得到一个50Ω的实部,但是这个实部并不是真正的电阻,因而不会产生噪声,所以很适合作为射频LNA的输入极。

3、高稳定度的LNA

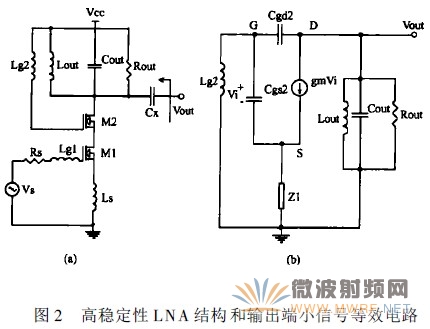

cascode结构在射频LNA设计中得到广泛应用,但是当工作频率较高时由于不能忽略MOS管的寄生电容Cgd,因而使得整个电路的稳定特性变差。对于单个晶体管可通过在其输入端串联一个小的电阻或在输出端并联一个大的电阻来提高稳定度,但是由于新增加的电阻将使噪声值变坏,因此这一技术不能用于低噪声放大器。

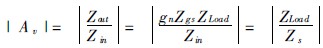

文献[3]对cascode结构提出了改进,在图1的基础上通过在M2管的栅极接上一个小值的电感Lg2就可以实现在增益不变的情况下,提高电路的稳定性,同时在M2管的漏极上接一个小值的电阻以调节电压增益如图2(a)所示。(b)所示的是小信号等效电路,其中Z1代表省略部分的等效阻抗,可以看到由于M2管的寄生电容Cgd2的值比较小,所以对于输出端阻抗而言,Lg2几乎可以忽略。因为放大器的增益等于输出阻抗和输入阻抗值之比,所以增加Lg2后并没有影响LNA的增益,电压增益为:

(4)

(4)

其中ZLoad=jwLout//(jwCout)-1//Rout,Zs是源端电感LS的阻抗。

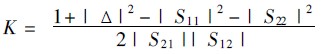

放大器的稳定系数为[3]

(5)

(5)

其中Δ= S11S22-S12S21 (6)

稳定系数K能快速给出稳定性判别依据,当K>1,|Δ|<1时,LNA将会无条件稳定。那么由公式(5)和(6)可知,若反向增益S12减小,那么K值将会增大,LNA将会增加稳定性。从图2(b)可以看到,由电感Lg2和MOS管的电容Cgd2组成一个低电阻通路使得从输出端反馈回来的信号流向接地端,从而降低了反向增益S12,提高了LNA的稳定度[3]。

4、偏置电流复用结构

现代无线通信设备要求具有更小尺寸,更轻重量,更长的待机时间。这就要求降低射频前端的电源电压,因此低电压、低功耗技术成为迫切需要。由公式(3)可知当输入端处于谐振时Ls=RsCgs/gml,其中Cgs是图1中M1管栅极和源极之间的电容,gml是M1管的跨导,则LNA的噪声系数为[4]:

(7)

(7)

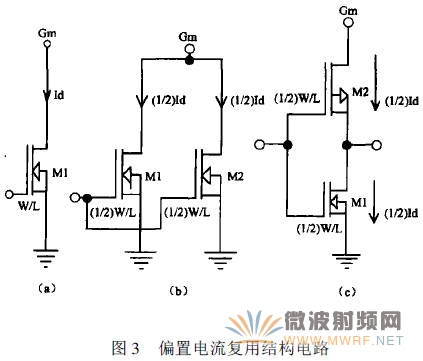

由(7)可知增大gml可以减小噪声系数。图1所示的cascode结构可以获得较小的噪声系数,但是往往需要比较大的漏极电流Id,增大了直流功耗。文献[4]中提出了偏置电流复用技术,其基本思想是:为了节省直流功耗,可以将PMOS管和NMOS管串联在直流偏置通路里,对其结构的说明如图3所示。

图3(a)所示的单个NMOS器件的宽长比和漏极电流Id都是(b)所示的单个NMOS的两倍,但由于两个NMOS并联,因此(a)和(b)具有相同的跨导值gm。(c)中的M2是PMOS管,且和(b)中的NMOS管具有相同的宽长比,由于PMOS器件的电子迁移率比NMOS稍低[2],所以gmc=(gml+gm2)

参考文献

[1] Pietro Andreani, Henrik Sjoland. Noise optimization o f an inductively degenerted CMOS low noise amplifier [ J ] . IEEE Trans. On Circuits and Systems, 2001, 48 ( 9) : 835 841.

[2] Thomas H . Lee. CMOS 射频集成电路设计[ M ] .北京: 电子工业出版社, 2002, 220 248.

[3] Seyed Hossein Miri Lavasani, Sayfe Kiaei. A new method to stabilize high frequency high gain CMOSLNA [ J ] . IEEE Conference on Circuits and Systems, 2003, 982 985.

[4] Andrew N. Karanicolas A 21 7 V 900 M Hz CMOS LNA and mixer [ J] . IEEE Journal of So lid state Circuits, 1998, 31 ( 12) : 1939 1944.

作者:杨国敏,肖高标