射频前端模块性能关系到整个接收机的性能。本文通过对接收机进行研究,分析了超外差接收机的特点,提出了一种采用PLL技术的接收机的射频前端方案,及对射频前端的关键技术指标进行了分析。并通过软硬件平台进行验证,实测本地振荡信号和接收机解调信号进行对比后表明系统指标达到要求。该射频接收前端具有高灵敏度、低噪声、稳定的中频输出、结构紧凑等特点,对其它移动通信终端(如GSM、CDMA)的研究有着非常重要的参考价值。

1、引言

现代无线通信始于19世纪末的无线电通信,在20世纪初到70年代,无线电通信技术得到发展和广泛应用,它为人类提供了一种崭新的通信手段。无线通信让人们实现了地球距离甚至是星球距离的通信,无线通信不只延伸了人类的通信距离,而且以电子技术、微处理技术进步为基础的无线通信技术的快速发展,也向人们昭示--以无限制自由通信为特征的个人通信时代是人类通信的未来[1]。

如何实现低成本、高性能的无线射频接收机终端是一项具有挑战意义的工作,无线射频接收机终端的设计对其它移动通信终端(如GSM、CDMA)的研究有着非常重要的参考价值[2]。它要求现在无线通信射频接收机在保证极高的灵敏度的前提下,尽可能的提高接收机的线性度,使信号失真最小,误码率最低,尽可能的展宽接收机的动态范围,使接收机的适应性更大,抗干扰能力更强。

2、接收机总体功能描述

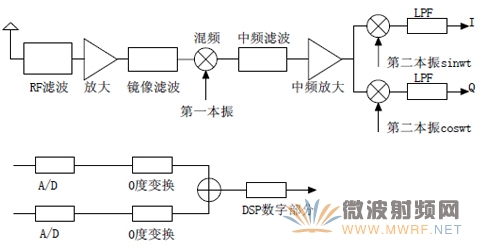

超外差结构自从1977 年由Armstrong 发明以来,已被广泛采用.超外差接收机[3]系统如图一所示:

图1、超外差接收机结构

接受到的信号在第一次下变频模块之前使用一个外部镜像干扰抑制滤波器,可以使镜像干扰大大削弱,达到一个可以忽略镜像频率的水平,在下变频以后使用中频滤波器可以进行正常的信道选择。第二次下变频后通常是解调出正交的两路信号,使得同相的和正交的两路信号在数字处理部分变得容易,在本设计中通过解调器将信号还原成I/Q 两路基带信号,并采用运算放大器进行放大输出。最后得到的信号可以送入ADC 中采样,经后级的DSP 处理恢复出原始信号。

在超外差式接收机中,第一次混频前的高频放大器必须是低噪声放大器,因为变频器的噪声系数一般都比较大,而RF 带通滤波器和镜频抑制滤波器是无源滤波器,有一定的损耗,按多级线性系统级联的噪声公式:

(1)

(1)

得知,如果没有低噪声放大器,则整个系统的噪声系数将很大。因此在变频器前引入具有一定增益的低噪声放大器可以减弱变频器和后面的中频放大器的噪声对整个系统的影响,从而对提高灵敏度有利。

超外差体系结构通过适当的选择中频滤波器和镜像滤波器可以获得极佳的选择性和灵敏度,被认为是最可靠的接收机拓扑结构,但需要付出一些成本以获得充分的性能。镜像干扰抑制和信道选择所需要的外部高Q 带通滤波器增加了成本和尺寸。本设计采用超外差式结构的接收机,主要是因为中频信号比载频低很多,在中频段实现对有用信道的选择要比在载频段实现信道的选择容易很多,对滤波器Q 值的要求低很多。另外,采用超外差接收机方案,将接收机的总增益分散到射频,中频和基带上,系统稳定性得以提高。

3、接收机关键部分的设计

3.1、接收机前端放大及混频电路的实现

本部分我们需要进行以下设计:

(1)低噪声放大器必须有很低的噪声,合适的增益,高的三阶互调截点及低的功耗[4]。

(2)混频器应有高的三阶互调截点及低的噪声。对本振信号的泄露抑制要好。

(3)好的灵敏度和高的动态范围。

LNA 采用AD 公司的ATF 系列低噪声放大器。低噪声放大器是射频接收机前端的主要部分。首先,位于接收机的最前端,就要求它的噪声越小越好。为了抑制后面各级噪声对系统的影响,还要求有一定的增益,但为了不使后面的混频器过载,产生非线性失真,所以它的增益又不宜过大。低噪声放大器必定是一个小信号线性放大器。所选取的低噪放工作带宽为450MHz 到6GHz,噪声系数在0~4GHz 内小于1 个dB,在2GHz 内小于0.5dB。

实测电路中LNA 的增益为18dB,噪声系数估算出小于1dB。

超外差接收机需要外接镜频抑制滤波器来滤除镜像频率干扰,因为镜像频率无法在中频滤波器中被滤掉,如果镜像干扰被混频后进入到带内,对有用信号的影响是非常大的,所以在本设计中为了消除镜像干扰,在变频器前加入了高Q 值的滤波器,同时还可以也可以滤除由于LNA 的非线性引入的各种互调失真干扰。

第一次下变频,采用性能指标稳定的SYM-25DHW 混频器,其插入损耗为9dB,三阶交调为30dBm。混频后采用的是高性能的SAW 滤波器,其具有体积小、抗电磁干扰性能好、频率选择性、温度稳定性能良好等突出优点。

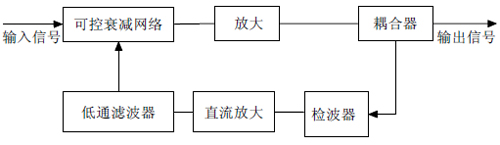

为了满足系统对动态范围和灵敏度的要求,信号在通过LNA 后,设计了增益控制链路。该链路由驱动放大器和AGC 构成。通过后端的功率检测,当小功率信号接收下来时,通过改变AGC 的控制电压减小衰减量,当大功率信号接收下来时增加衰减值,以提高接收机的动态范围指标。如下图所示:

图2、AGC 电路原理图

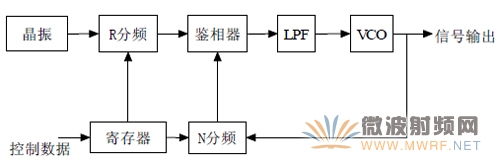

3.2、接收机本振锁相环路的设计

图3、琐相环原理图

接收机通过混频实现射频变频到基带,而且采用的是超外差式结构的接收机,因此在本设计中我们需要设计两个本振源。系统设计要求本振信号频率精度和稳定度高,相位噪声小,所以选择锁相环实现本振生成。锁相环是一种建立在相位负反馈基础之上的闭环控制系统[5],对相位噪声和杂散具有很好的抑制作用,在电视,仪器,通信等领域得到了广泛的应用。该接收机本振设计我们采用ADI 公司的琐相环系列芯片[6-7]做本振的设计,其可应用于无线射频通信系统,是性价比很高的电荷泵锁存芯片。

在设计中,通过编写程序由单片机实现提供给琐相环的CLOCK,DATA 和LE 信号,在频率合成器芯片内部完成参考晶振R 分频和压控振荡器N 分频相位的比较,并且转换成相应的线性电压后,经过3 阶环路滤波器滤出高频干扰信号后,得到一个稳定电压来控制压控振荡器的输出,最终的信号频率通过两个锁相芯片被分别锁定在第一和第二本振频率上。

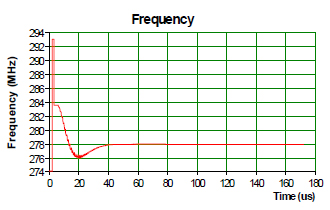

图4、第二本振的琐相环入琐过程

从图4,第二本振的入锁过程我们可以看到琐相环的入锁时间在40us 左右,满足要求。采用单片机提供锁相的控制字的优点就在于:利于及时修改,便于操作。下面是本振的实际电路图,包括第一本振锁相芯片和第二本振锁相芯片,其共用一个10MHz 的晶振:

图5 实际的第一、第二本振电路图

3.3、解调

接收机解调部分采用AD 公司的解调芯片,该芯片工作频率从50MHz 到1000MHz,包括正交下变频器,内置可控增益放大器和偏置电路。其内置VGA,控制电压由外部提供并可调增益大小,增益可调范围为44dB。

输入芯片的中频信号为了满足芯片的输入功率要求,加入了功率驱动放大链路,经放大后输入解调芯片的功率约为-40dBm 左右。因为解调芯片对第二本振信号内置了二分频器,所以第二本振信号频率应该是所需频率的两倍。

输出的I/Q 两路信号分别再经过运放电路进行放大,最终输出给数字基带部分进行处理[8-9]。

4、实际测试结果

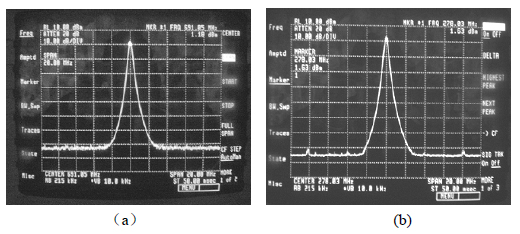

实际测时,输入信号频率为831MHz,通过在单片机编写控制字程序设置第一本振和第二本振的输出频率,第一次混频后得到的中频信号频率为140MHz,第二次混频后解调输出频率为1MHz 的I/Q 两路信号。本振的输出信号如下图所示:

图6、(a)第一本振输出(b)第二本振输出

可以看到锁相环完成频率锁定,第一本振锁定在691MHz,因为解调芯片对第二本振信号内置了二分频器,故第二本振设计锁定在278MHz。从图中可知输出信号杂散均小于-70dBc,锁相芯片在它要求的频率上工作正常,设计的结果也符合了系统对PLL 本振电路的要求。在锁相环输出信号之后,加入一个衰减网络,使输入到混频器和解调芯片的本振信号功率满足器件输入功率要求。

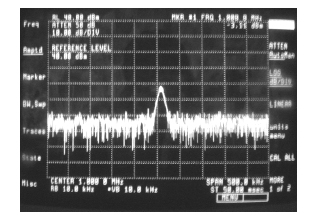

接着对整机进行测试,结果如下:

图7、实际解调输出信号

解调输出后得到信号频率为1MHz 的基带信号。固定AGC 增益值的情况下,即此时衰减值固定为0dBm,改变输入射频信号的功率,每增加10dBm,输出I/Q 信号功率增加约为10dBm,整机线性度[10]良好,注意此时应该在较低功率范围内调节输入功率,保证输出I/Q信号功率不会过大。经测试,接收机的最小可接收检测信号功率约-118dBm。

在接收机中,解调输出I/Q 两路平衡是非常重要的指标。由于接收机信道特性不同,本振信号相位误差等诸多的因素都会导致I/Q 两路基带信号增益不平衡。若I/Q 失配,则会导致I/Q 误码率增高,严重影响解调性能。在本设计中,在选取芯片、设计电路中充分考虑到此问题,实际I/Q 两路输出基本做到了平衡输出。

5、结论

本文研究了使用PLL 的接收机原理和实现方案,并成功的用软硬件平台对其实现。本文的创新点在于成功的运用两个锁相环电路实现第一、二本振信号,试验结果表明锁相环有锁定时间短,相位噪声小,性能稳定等优点。实测结果表明接收机性能良好,指标达到了系统设计要求。

现代射频接收机主要是向高线性、大动态范围,高灵敏度,高分辨率等方面发展。如何采取有效的方法来提高接收机的抗干扰能力,降低超外差式接收机的成本,使得整体性能得以改进,是当今研究的热点方向,对接收机的研究有着非常重要的意义。

作者:牛吉凌,孙利佳

参考文献

[1] Roy B.《无线通信技术》[M].北京:科学出版社,2004.

[2] 张玉兴.《射频模拟技术》[M].北京:电子工业出版社,2001.

[3] 陈邦媛.《射频通信电路》[M].北京:科学出版社,2002.

[4] 张猛,章策珉,马金军,楼东武.射频接收机整体噪声与增益可预测性设计[J].无线电工程, 2000,1(2): 13-17.

[5] 张厥盛,郑继禹.《锁相技术》[M].西安:西安电子科技大学出版社,1996.

[6] Behzard R, [M]. Prentice Hall PTR, 1998.

[7] Integrated synthesizer and VCO ADF4360-8, Analog Devices C04414-0-12/04(B), 2004.

[8] Derek K S, The design and implementation of low-power CMOS radio receivers [J]. PhD Thesis, 1998, 17(2):41-46.

[9] Reinhold L P, [M].北京:科学出版社,2002.

[10] Gonzalez G, Micro transistor amplifiers: analysis and design [J]. Englewood Cliffs, NJ: Pretice-Hall, 1984:91-44.